4 月 16 日,据韩媒报道,三星电子计划最早于 2026 年 5 月完成首批下一代高带宽内存 HBM4E 的样品生产,并在内部验证后交付给英伟达。

三星电子的目标是抢占下一代HBM市场。

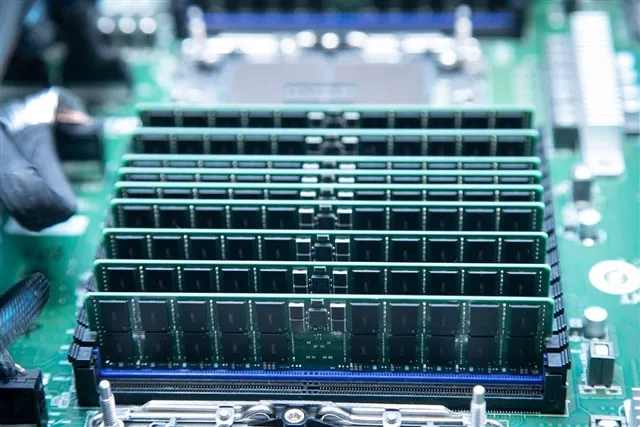

从技术路线看,HBM4E延续了HBM4的整体架构,但在性能和带宽上提升了不少。

其逻辑芯片采用 4nm 工艺制造,DRAM 部分则基于 10nm 级第六代(1c)工艺。接口位宽达到 2048 位,数据传输速率提升至 16 Gb/s。在多堆栈系统中,整体内存带宽最高可达 24.6 TB/s。

图源:朝鲜商报

每个堆栈的独立通道数量增加至 32 个,每个通道还包含 2 个伪通道,使得数据访问更加灵活高效。

同时,HBM4E 还引入了定向刷新管理(DRFM)等机制,用于提升可靠性、可用性和可维护性,并对行锤击等问题进行优化处理,进一步增强系统稳定性。

在上一代HBM4芯片的竞争中,三星率先实现了量产,领先于竞争对手SK海力士和美光。

这次HBM4E中,SK海力士也正全力投入,并考虑采用比HBM4先进一代的DRAM产品,优先采用台积电的3nm工艺制造逻辑芯片。

图片来源:DIGITIMES

此前,SK海力士在HBM4逻辑芯片上采用的是台积电12nm工艺,而HBM4 DRAM则采用的是10nm的第五代(1b)工艺。

目前HBM4 和 HBM4E 的主要应用平台——英伟达 Vera Rubin 系列 AI 芯片,发布时间有所调整,整体产量规划也在动态变化,但并不影响存储厂商的布局节奏。

消息数据来源:朝鲜日报、韩国商业报