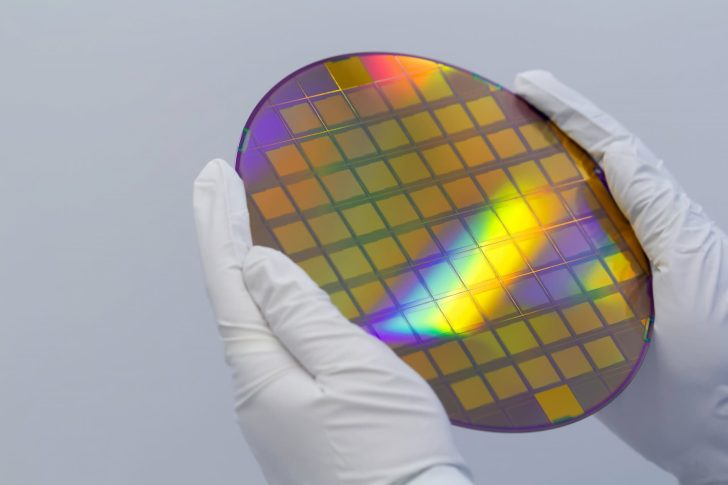

就在行业还在热议3nm工艺量产进展时,台积电已经悄悄把2nm技术推到了关键门槛!

根据《经济日报》最新报道,台积电目前2nm芯片的良品率已突破90%。

能取得这样的进展,关键在于架构上的变革。2nm工艺不再使用过去3nm和5nm常见的FinFET(鳍式场效应晶体管)架构,而是采用了基于GAA(环绕式栅极)技术的MBCFET结构。

通俗点说,原本像“单行道”的电流通道被升级成了“立体立交桥”,有效解决了制程微缩带来的漏电难题。

此外,台积电在纳米片堆叠技术上的多年深耕,再加上极紫外光(EUV)设备的加持,使得2nm制程的整体良率在短时间内实现大幅提升。去年7月刚启动2nm风险试产时,良率还只有60%左右,如今短短半年已攀升至90%以上,成长速度惊人。

供应链消息指出,台积电可能在今年下半年正式启动2nm的量产准备。目前,其在新竹宝山区建设的四座超级晶圆厂(占地超过90公顷)也已进入冲刺阶段,预计将在2025年全面量产。

从订单情况来看,2nm芯片市场的前景已经被验证。台积电目前收到的2nm订单数量已是当年5nm初期的四倍。作为配套,晶圆切割厂商 Kinik 已紧急扩充研磨工具产能至每月5万片,为2nm芯片的推进全力配合。

图源:wccftech

而在海外,台积电位于美国亚利桑那州的N4制程工厂也在加快脚步。当前该厂月产能已达1.5万片,未来还将提升至2.4万片,基本处于满载状态。

苹果、英伟达、高通、博通等美国科技公司都是该厂的主要客户,英伟达的AI芯片就在此处进行工艺验证,预计将在年底前量产。

不过,美国本土制造成本高,已有传闻称,亚利桑那工厂的代工报价或将上涨30%。

即便如此,客户依然愿意为先进制程买单。台积电总裁魏哲家曾总结,制程每推进一代,芯片性能可提升30%-40%,能耗则下降20%-30%,这种提升是当前算力增长不可替代的路径。

除了2nm之外,台积电也早已布局1.4nm乃至更先进的技术路线图。可以说,随着2nm良率的突破,芯片制造正迈入一个以“高质量”为导向的新阶段。

消息来源:《经济日报》-“台积电 2 纳米工艺产量突破 90%,美国亚利桑那州工厂产能接近 100%”