CMOS系列或HC系列器件的输入阻抗很高,在使用中除容易引起静电干扰外,还容易传输反射波干扰。因此在长线传输使用时需要注意采取相应措施来抑制或削弱反射波,本文从降低阻抗和长线驱动两个方面,提供了5个解决方法。

1、阻抗匹配

根据反射理论,当传输线的特性阻抗与负载电阻相等时,反射将不会发生。即阻抗不匹配是造成信号在传输线上反射的原因。实际的电路实现中阻抗不匹配是绝对的,而匹配是相对的。

引起阻抗不匹配的原因有多种,由驱动源、传输线和负载的阻抗不同可引起阻抗不匹配、传输线的不连续,例如导通孔、短截线也可引起阻抗不匹配;另外由于返回路径上局部电感、电容的变化、返回路径不连续也会导致阻抗不连续。其中,由驱动源、传输线和负载的阻抗不同引起的阻抗不匹配是最主要的原因。

阻抗匹配方法有以下几种:

2、采用输入/输出驱动器

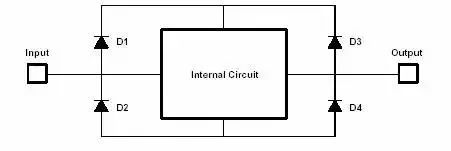

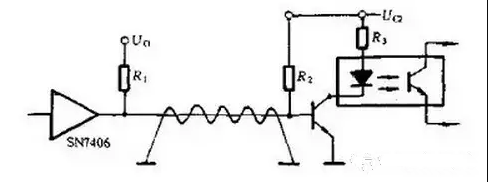

如下图所示

当A点为低电平时,反射波从B向A传输。由于此时驱动器的输出阻抗几乎为零,反射信号一到达该输出端就有相当部分被吸收掉,只剩下部分信号继续反射。也就时说,由于反射信号遇到的时低阻抗,它的反射能力大大减弱。当A点为高电平时,发送器的输出阻抗很大,可视为开路,为了降低接收器的输入阻抗,接入一个负载电阻,这样就大大削弱了反射波的干扰。

3、降低输入阻抗

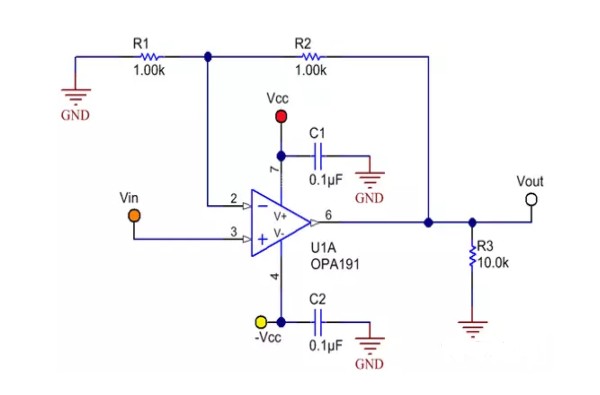

如下图所示

当驱动器输出低电平时,A点对地阻抗很低;当驱动器输出高电平时,B点对地阻抗也很低。由此可见,无论是输出高电平还是低电平,反射波都将很快衰减。

4、采用光电耦合

除可有效抑制反射波干扰外,还实现了信号地隔离。

5、采用差分传输技术

使用差分信号进行长线传输有一个很重要的原因是噪声以共模的方式在一对差分线上耦合出现,并在接收器中相减从而可消除噪声。

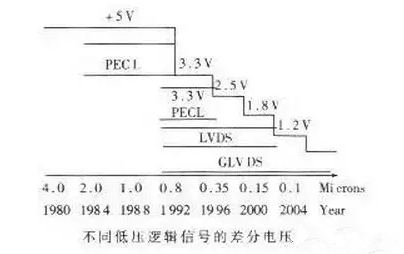

常用的差分传输技术有ECL、PECL、LVDS及GLVDS.

ECL和PECL技术的信号摆幅依赖于供电电压,ECL要求负的供电电压,PECL使用正的供电电压。GLVDS是一种发展中的尚未确定的新技术,使用500mV的供电电压可提供250mV 的信号摆幅。

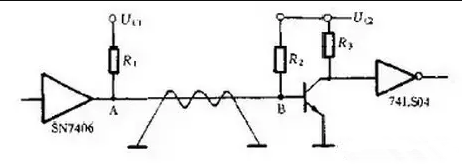

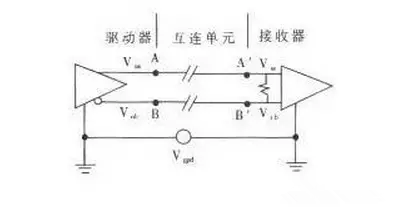

LVDS物理接口使用1.2V偏置提供400mV摆幅的信号,其驱动器和接收器不依赖于特定的供电电压。LVDS驱动器由一个驱动差分线对的电流源组成,通常电流为3.5mA,接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mA 的电压。当驱动器翻转时,它改变流经电阻的电流方向,因此产生有效的逻辑″1″和逻辑″0″状态。低摆幅驱动信号实现了高速操作并减小了功率消耗,差分信号提供了适当噪声边缘和功率消耗大幅减少的低压摆幅。终端电阻100Ω,不仅终止了环流信号,同时防止信号在终端发生反射。如下图所示:

差分传输方式的终端匹配方法比较:

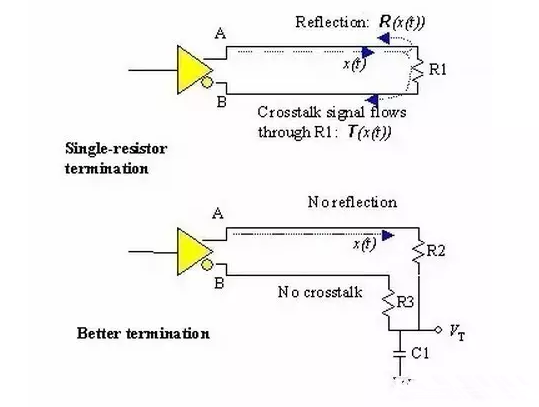

如下图所示的两种差分传输方式的终端方法,第一种方法采用单电阻终端,第二种方法采用双电阻终端。

第一种方法对差模信号进行匹配,但不对共模信号匹配。在共模干扰比较理想的情况(干扰信号同时到达A、B线,并且幅度相同)下可以很好的工作,但由于布线等原因造成A、B传输线受干扰情况不完全一致时,干扰信号会在传输线上来回反射,特别是在传输时钟信号,并且传输线延时等于1/4时钟周期时,干扰信号可能在线路上来会反射形成自激。

第二种方法对每条传输线单独进行匹配,该方法对共模信号和差模信号同时匹配,故不会在传输线上产生反射。