瑞萨MCU杯第八届立创电子设计开源大赛正式落幕,最终获奖项目正式出炉!本文介绍的是:本届大赛三等奖项目《基于RISC-V内核的生理信号加速SoC及FPGA的原型设计》。

本文作者:瑞萨MCU杯第八届立创电子设计开源大赛选手@buck_boost,禁止商用,未经许可禁止转载。

1、项目功能介绍

本项目设计了一种应用于心脏骤停场合的智能生理信号分析加速SoC,采用基于卷积神经网络算法和近似熵算法的组合算法程序以实现心电分类诊断和减少室颤误判的效果。本项目自研了一套生理信号专用的MCU级别的SOC开发板,专门用于部署生理信号的分析。该开发板不仅仅能用于除颤仪,也可以用在绝大多数需要处理生理一维信号的医疗器械上。

本项目所设计的开发板包含的功能有:熵计算加速、CNN 计算加速、定点浮点乘法加速等。可以将原本在单片机上需要数秒乃至数小时计算完成的熵算法以及一维卷积神经网络算法加速到单片机算力可以接受的水平。

本项目设计的开发板采用 RISC-V 指令集的 CPU内核,其型号为 E203,并自主设计了生理信号处理专用协处理器。协处理器包含熵计算加速器、向量乘法计算加速器、定点乘法加速器、浮点乘法器等等生理信号加速专用电路。在本SOC配套的 SDK测试中,进行了250点的近似熵计算,对于纯软件计算,提速约 34 倍,利用加速器计算部分提速约 1700 倍。在一个典型的 CNN心电识别网络中,利用加速版本计算的程序提速约 33 倍。

2、硬件部分

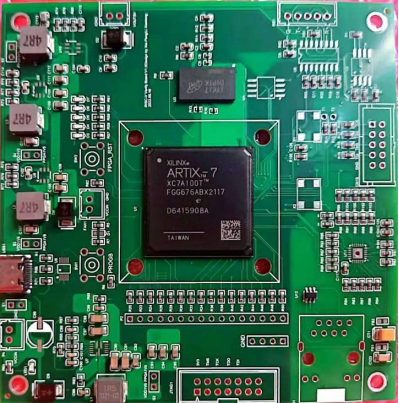

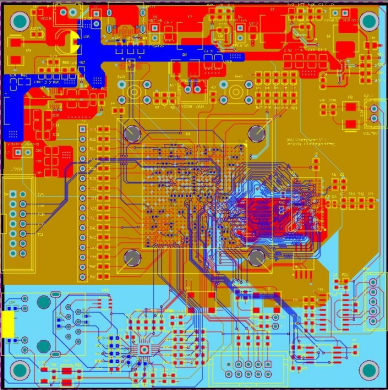

为了验证SOC的相关功能,本文特别设计了功能完整的 FPGA 验证板。如图 3 所示,该验证板主要由电源模块、flash、DDR、晶振、通信串口等部分组成。能够与心电采集模块和电除颤电路通信并共同完成自动诊断和电除颤抢救任务。为了保证 FPGA 和 DDR 能正常工作,其电源模块可以提供 1V、1.5V、1.8V、3.3V 等电压,并严格按照 FPGA 上电顺序的要求上电。

实物图

原理图

3、软件部分

本项目利用熵和 CNN 设计了一种融合算法,其区别于传统心电分类程序,能在胸外按压过程中防止误判心电信号为室颤,以达到提高救治效率的效果。由于生理系统具有明显的非线性性质,因此非线性分析方法可能有助于更好地揭示其特性与机理。从工程技术上看,常常需要研究信号性质的动态变化,因而十分需要只要较短数据就能表现信号特点的动力学参数。从这一要求上看,Rncus 在1991 年提出的近似熵(Apporxiantte Entopy,简记ApEn)是一个值得注意的参数。故本文选用近似熵算法作为诊断手段之一。

此外,本项目还结合了卷积神经网络(CNN)算法,可以对心电信号做进一步地分类。本文所述的自动心电诊断模块区别于传统 CNN 方法,采用 CNN 与熵值判定相结合的方式,提升了在急救场合中对含有同频段伪迹噪声的心电分类准确率。

传统的心脏骤停急救设备往往在施救者在进行胸外按压的时候不进行 ECG 的自动诊断,且在自动诊断的时候要求施救者中断胸外按压,影响抢救效率。其原因在于胸外按压会产生严重的伪迹,该伪迹的频谱与正常心电的频谱大幅度重合,采用传统算法难以滤除。本文中的设计采用卷积神经网络算法和近似熵算法结合的方式,可利用二者的优势,规避二者的缺点。由于心肺复苏过程中的心电信号数据难以获取,因此难以找到足够的数据给神经网络训练。在缺少足够训练集的情况下,依靠人为加噪难以提高室颤的识别准确率,而单独通过熵来判断室颤只能进行二分类且抗干扰性能差。

该算法可以高效利用协处理器,本文基于该算法自主设计了一套 CNN 以及近似熵计算库,可以通过搭载本文所设计的协处理器的 CPU 运行。

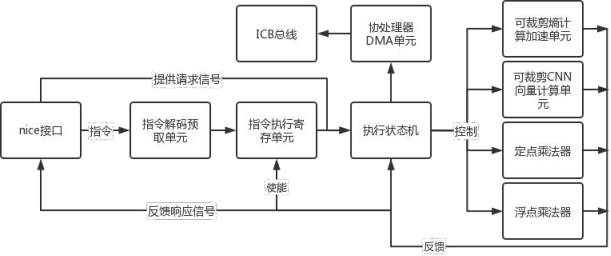

本设计采用 E203 内核作为 SOC 的 CPU,利用 nice 接口扩展协处理器。协处理器由指令解码单元、执行状态机、熵计算加速单元、CNN 向量计算单元、单周期定点乘法器组成,设计框图如下图 所示:

协处理器总体设计框图

当程序调用协处理器时,CPU 会拉高 nice 接口的 nice_req_valid 信号线请求握手,协处理器在空闲的情况下会将 nice_req_ready 拉高完成握手,并从指令预取单元中获取指令,状态机会根据指令解码单元解码出的数据和指令调用相应的执行单元执行指令,指令执行完成后,状态机会把 nice 接口的 nice_rsp_valid 线拉高请求握手。

协处理器指令集以及指令解码单元的设计

E203处理器的nice指令编码如表所示:

nice指令编码

|

比特位 |

31-25 |

24-20 |

19-15 |

14 |

13 |

12 |

11-7 |

6-0 |

|

功能 |

func7 |

rs2 |

rs1 |

xd |

xs1 |

xs2 |

rd |

opcode |

其中,func7为指令编码空间,最多支持额外译码出128条指令;rs2和rs1为寄存器索引;xd指示该指令是否需要将结果写回至rd索引的寄存器;xs1和xs2分别指示是否需要读取rs1和rs2索引的寄存器;opcode是操作码。指令解码单元由组合逻辑电路和一个D触发器组成,其逻辑框图如图所示:

指令解码单元的设计框图

协处理器支持执行指令的同时预取一条指令,通过相等比较器判断指令的各部分是否有效,将判断信号送入与门获得某指令的预取信号。在协处理器成功握手后,通过D触发器输出该指令的执行信号。该逻辑可以保证协处理器可以在一条指令执行完成后立即执行下一条指令。

协处理器一共设有7条指令,如下表所示:

协处理器的指令集列表

|

指令 |

操作数1 |

操作数2 |

写回值 |

功能 |

|

custom_lbuf_apen |

地址 |

无 |

1 |

熵计算加速器写入原始数据 |

|

custom_lth_apen |

阈值 |

无 |

2 |

熵计算加速器写入阈值 |

|

custom_calu_apen |

写回首地址 |

无 |

3 |

熵计算加速器工作一次 |

|

custom_lker_cnn |

卷积核首地址 |

卷积核长度 |

4 |

CNN向量计算单元加载卷积核 |

|

custom_calcu_cnn |

序列首地址 |

无 |

结果 |

CNN向量计算单元计算一次 |

|

custom_multi |

变量1 |

变量2 |

积 |

进行一次定点乘法计算 |

|

custom_multi_f |

变量1 |

变量2 |

积 |

进行一次浮点乘法计算 |

其中,熵计算加速器具有三条操作指令,分别为custom_lbuf_apen、custom_lth_apen、custom_calu_apen。程序进行熵计算时,首先需要调用custom_lbuf_apen指令将待计算熵的序列的首地址写入熵计算加速器,然后调用custom_lth_apen指令设置熵计算中的阈值,随后不断调用custom_calu_apen指令获取计算结果。

CNN向量计算单元一共有两条指令,分别为custom_lker_cnn、custom_calcu_cnn。卷积神经网络推理程序在进行卷积乘法运算时,调用custom_lker_cnn将卷积核加载进单元,随后不断调用custom_calcu_cnn计算向量乘法以达到卷积计算的目的。

由于在绝大多数信号的处理算法中,需要大量的乘法运算,而本文使用的CPU内核属于低功耗CPU,没有单周期乘法器和浮点计算单元,为了防止乘法计算拖累算法整体计算速度,影响协处理器的加速效果,本文为协处理器添加了两条乘法指令用于定点和浮点计算:custom_multi、custom_multi_f。

执行状态机的设计

本文所设计的协处理器包含多项功能,虽然其功能差别巨大,但是每个功能的执行状态总可以分解为表3中8个状态的一个,因此,协处理器的所有指令通过指令执行信号复用8个状态。

执行状态机的8个状态

|

状态 |

执行功能 |

|

IDLE |

执行状态机处于空闲状态,此时状态机等待预取指令。 |

|

LOAD |

执行状态机Load地址操作数。 |

|

READ |

执行状态机通过ICB总线读取数据。 |

|

WREG |

执行状态机向子单元的寄存器写入数据。 |

|

CALU |

执行状态机操控子单元进行计算。 |

|

WAIT |

执行状态机等待子单元计算完成或者数据稳定。 |

|

WMEM |

执行状态机通过ICB总线写入数据。 |

|

RSP |

执行状态机拉高nice_rsp_valid请求握手。 |

状态机采用三段式编写,状态跳转采用组合逻辑电路实现,状态输出采用时序逻辑电路实现,状态机大致工作逻辑如下所述。

1、当状态机处于IDLE状态时,状态机会等待nice接口的nice_req_ready信号拉高,随后根据预取的指令类型跳转到下一个状态;

2、当状态机处于LOAD状态时,状态机会将地址预加载到DMA单元,同时拉高nice_mem_holdup,随后跳转到READ状态;

3、当状态机处于READ状态时,状态机会通过DMA从ICB读取指定长度的数据,随后根据指令寄存器的内容跳转到RSP或者WAIT状态。

4、当状态机处于WREG状态时,状态机会根据指令向子单元的寄存器写入数据,随后跳转到RSP状态。

5、当状态机处于CALU状态时,状态机会根据指令向子单元的寄存器写入数据,随后根据指令寄存器的内容跳转到WAIT或者RSP状态。

6、WAIT状态用于等待子单元计算完成或者数据稳定。该状态使用移位寄存器进行计数,通过判定某一位是否为1判断是否需要继续等待,随后根据指令寄存器的内容跳转到WMEM或者RSP状态。

7、当状态机处于WMEM状态时,状态机会通过DMA单元向ICB总线写入计算结果数据,随后跳转回到CALU状态进行下一条计算。

8、当状态机处于RSP状态时,状态机会向nice_icb_rsp_rdata寄存器写入指令写回值。随后跳转到IDLE状态结束一条指令的执行。

可裁剪熵计算加速单元的设计

熵计算加速单元的架构如图所示:

熵计算加速器的架构

熵计算加速单元包含向量计算单元阵列、并行计算控制器、向量重构器、寄存器组以及读写控制器。其对外接口如表所示:

熵计算加速器的对外接口

|

接口名称 |

位宽 |

接口功能 |

|

clk |

1 |

加速器模块的时钟端口 |

|

rst_n |

1 |

加速器模块的复位端口 |

|

reg_cs |

1 |

加速器模块寄存器读写使能端口 |

|

reg_wr |

1 |

加速器模块寄存器的写有效端口 |

|

reg_rd |

1 |

加速器模块寄存器的读有效端口 |

|

reg_wr_addr |

10 |

加速器模块寄存器的写地址端口 |

|

reg_rd_addr |

10 |

加速器模块寄存器的读地址端口 |

|

reg_data_in |

32 |

加速器模块寄存器的数据输入端口 |

|

reg_data_out |

32 |

加速器模块寄存器的数据输出端口 |

熵计算加速单元的控制完全通过读写寄存器完成,加速器内部寄存器组的寻址范围为0-(APEN_DATA_LEN+1),其中APEN_DATA_LEN是向量计算单元的个数,可以通过修改APEN_DATA_LEN这个参数裁剪熵计算加速器。数据寄存器组的地址范围为0-(APEN_DATA_LEN-1),这个寄存器组的作用是存储待计算的原始数据序列。由于这个寄存器组数量较多,为了保证运行效率,不可以采用CPU依次读写的方式,需要通过DMA写入。地址为APEN_DATA_LEN的寄存器是阈值寄存器。其寄存的是熵算法中的阈值。

控制寄存器和状态寄存器共用地址APEN_DATA_LEN+1,控制寄存器只写,状态寄存器只读。控制寄存器和状态寄存器的功能编码如表所示:

控制寄存器的功能编码

|

比特位 |

31-12 |

11 |

10-1 |

0 |

|

功能 |

保留 |

计算维度(0为2维,1为3维) |

计算编号 |

写1电路开始工作 |

状态寄存器的功能编码

|

比特位 |

31-23 |

22-13 |

12 |

11 |

10-1 |

0 |

|

功能 |

保留 |

向量距离大于阈值的个数 |

保留 |

计算维度 |

计算编号 |

是否空闲 |

外部电路在调用熵计算加速单元计算前,需要向控制寄存器对应位置写入必须要的计算信息,并在最低位写1。加速单元检测到控制寄存器的最低位为1后,会立即开始一次计算,同时将控制寄存器的最低位写0,状态寄存器的最低位写1。完成计算后,加速单元会重新把状态寄存器的最低位置0。

模块还自带一个由组合逻辑电路设计的向量重构路由器,其作用是将原始数据序列重构成2维或者3维的向量组。并根据控制寄存器中的计算编号,提供相应的数据给距离计算单元。

向量距离计算单元设计

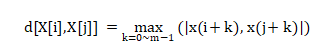

近似熵算法中,向量距离的定义如式所示:

其中X是重构后的m维向量组,x是原始序列,d是向量之间的距离,则距离为向量X[i]、X[j]中对应元素差值的绝对值最大的一个。

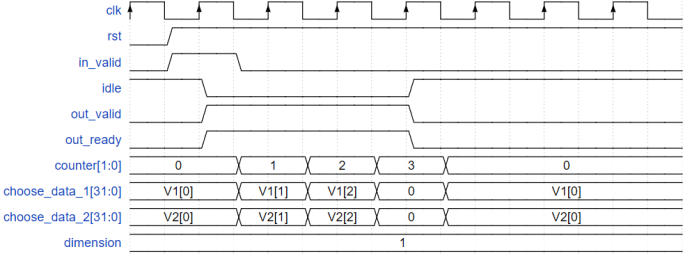

向量距离计算单元由两级流水线组成。流水线的第一级是数据选择器,其功能是选择数据输出给下一级,以3维向量距离计算为例,其工作时序如图所示:

向量距离计算单元流水线第一级时序图

外部电路通过拉高in_valid激活流水线第一级工作。此时该流水线会把idle线拉低,指示外部电路本级流水线忙。若和下级流水线握手成功,则会根据计数器输出待计算的数据给流水线下一级。

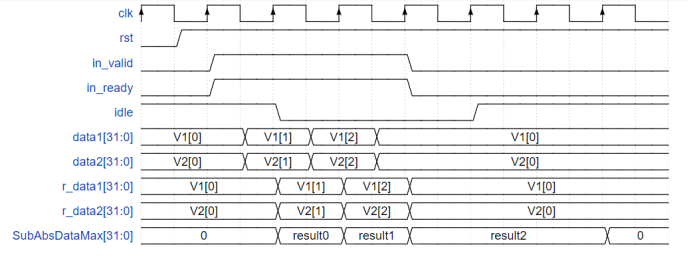

流水线的第二级是计算电路,其功能是找到第一级流水线工作周期内所提供数据的差的最大绝对值,这个最大绝对值就是向量的距离。时序图如图所示:

向量距离计算单元流水线第二级时序图

流水线的第二级电路在和第一级电路成功握手后,会依次根据第一级电路送入的数据算出元素差值的绝对值最大的一个。当其in_valid线被拉低后,计算结果将会被锁存1个时钟周期。

可裁剪一维CNN向量计算单元的设计

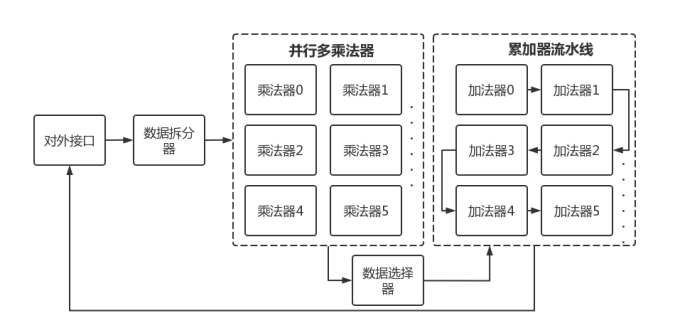

向量计算单元的架构如图所示:

向量计算单元的架构

由于E203的ICB总线的带宽限制,采用并行计算的方法并不能有效提高计算效率,因此,本设计在向量计算单元上放弃多单元并行计算而采用长流水线计算的方法。该单元由对外接口、数据拆分器、并行多乘法器、数据选择器、累加器流水线组成。

向量计算单元的流水线和对外接口设计

该单元的对外接口每次只提取一个数据,因此一个时钟周期只会产生一个乘法结果,因此需要流水线进行累加处理。并行多乘法器每执行完成一次后,数据选择器将会筛选出有用的数据送入累加流水线。

向量计算单元的对外接口如表所示:

向量计算单元的对外接口

|

接口名称 |

位宽 |

接口功能 |

|

sclk |

1 |

加速单元的时钟 |

|

Seq_ori |

DATA_WIDTH * MAX_CONV_KERNEL_LEN |

原始序列 |

|

Seq_ker |

DATA_WIDTH * MAX_CONV_KERNEL_LEN |

卷积核序列 |

|

KernelLen |

8 |

卷积核的长度 |

|

Datavalid |

1 |

数据有效 |

|

Result |

DATA_WIDTH |

卷积计算结果 |

其中DATA_WIDTH是乘法器的数据位宽,MAX_CONV_KERNEL_LEN是向量计算单元支持的最大卷积核长度,可以通过修改MAX_CONV_KERNEL_LEN达到裁剪向量计算单元的目的。

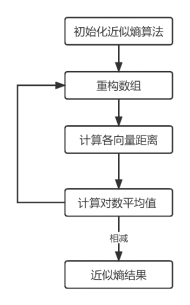

近似熵计算库设计

近似熵库具体计算流程如图所示,计算前需要进行初始化处理,即赋值比例、计算标准差和阈值。之后进行数组的重构,即重构m维度数组(共有n-m+1个m维度向量)和m+1维度数组。随后计算m维和m+1维向量的距离,并求得对平均值。最后对平均值做差,得到近似熵的结果,可根据该结果判断病人的身体状态。

近似熵计算流程图

CNN推理库设计

CNN库采用C语言编写,采用面向对象的思想进行编程。每个CNN网络将定义为一个C结构体,实例化的时候设置其参数即可自动化地进行推理。CNN结构的定义如下:

typedef struct CNN_NET

{

int LayerAmount;

int kernelAmount[CNN_LAYER_MAX];

int kernelLen[CNN_LAYER_MAX];

int PoollingMode[CNN_LAYER_MAX];

int PaddingAmount[CNN_LAYER_MAX];

CALU_TYPE* pOriginalData;

int OriginalDatalen;

CALU_TYPE* Kernel0BuffStartAddr[CNN_LAYER_MAX];

}CNN_NET;

其中,LayerAmount代表CNN网络的层数;kernelAmount数组存储每层的卷积核数量;kernelLen数据存储每层的卷积核长度;PoollingMode数组存储每层的池化方式;PaddingAmount数据存储每层的预padding数量;pOriginalData是一个指针,指向原始数据序列的数组;OriginalDatalen是原始数据序列的长度;Kernel0BuffStartAddr是一个指针数组,用于存储每层卷积核的起始地址。

CNN推理库暴露给用户的函数有:

void CNN_RunAllLayer_inst(CNN_NET* Net_inst);

void CNN_Calurelu(CALU_TYPE* NetBuff, int len);

CALU_TYPE CNN_Calculate_Full_Connection(CALU_TYPE* NetBuff, CALU_TYPE* ParaBuff, int len);

其中,CNN_RunAllLayer_inst函数是根据CNN_NET示例化后的变量配置自动依次计算各个卷积层,CNN_Calurelu函数是计算relu激活函数,CNN_Calculate_Full_Connection函数用于计算全连接层。

本推理库的卷积部分采用乒乓机制存储临时数据,规避传统CNN推理库动辄采用动态内存的方法,更适合在无操作系统的单片机上运行。其包含的API函数有:

int Conv_SetPaddingLen(int PaddingLen);

int Conv_SetStride(int stride);

int Conv_SetSeqLen(int len);

int Conv_LoadOriSeqToCache(CALU_TYPE* OriDataBuff, int OriDataLen);

int Conv_LoadKernel(CALU_TYPE* KernelBuff, int KernelLen);

void Conv_ClearConvCache(void);

int Conv_RunningConvolution(int StartPoint);

int Conv_RunningPooling(int PoolingMode, int PoolingLen);

void Conv_LayerEnd(void);

其中,Conv_SetPaddingLen函数的功能是设置Padding长度;Conv_SetStride函数的功能是设置卷积步长;Conv_SetSeqLen函数的功能是设置原始序列长度;Conv_LoadOriSeqToCache的功能是加载原始数据序列;Conv_LoadKernel函数的功能是加载卷积核; Conv_ClearConvCache函数的功能是清零缓存;Conv_RunningConvolution函数的功能是进行一层卷积运算;Conv_RunningPooling函数的功能是进行一层池化运算;Conv_LayerEnd函数的功能是结束一层运算。

功能仿真和整体测试结果

SOC验证和测试

将工程综合成比特流载入型号为XC7A100T的FPGA开发板中。编写一个卷积神经网络测试心电的用例和近似熵计算测试用例,每个测试用例均有纯软件版本和调用加速器的版本,

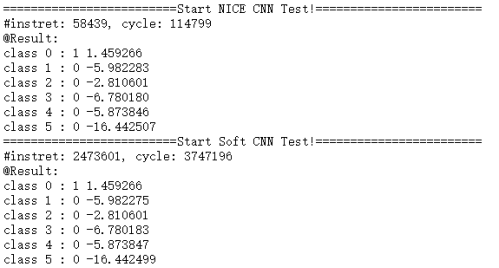

其中CNN心电分类的测试结果如图所示:

CNN心电分类的测试结果

CNN采用两层网络结构,原始数据是1000点采样率200Hz的心电采样序列,第一层网络是卷积层,采用1个长度为9的卷积核,第二层是全连接层,参数序列长度为992。测试结果表明,在这个简单卷积神经网络的测试中,硬件加速版本的程序相比纯软件计算版本的程序提速约33倍。这意味着在低功耗单片机上难以实时运行的神经网络心电分类程序,在本SOC上仅仅只需要几毫秒。

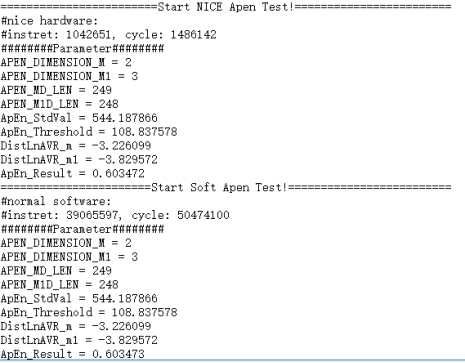

近似熵算法的测试结果如图所示:

近似熵算法的测试结果

该近似熵计算程序采用250点序列,测试结果表明,在采用该算法的近似熵计算测试中,硬件加速版本的程序相比纯软件计算版本的程序提速约34倍。在16M主频下,协处理器将原本需要数秒计算时间的250点近似熵算法优化到了区区几十毫秒。

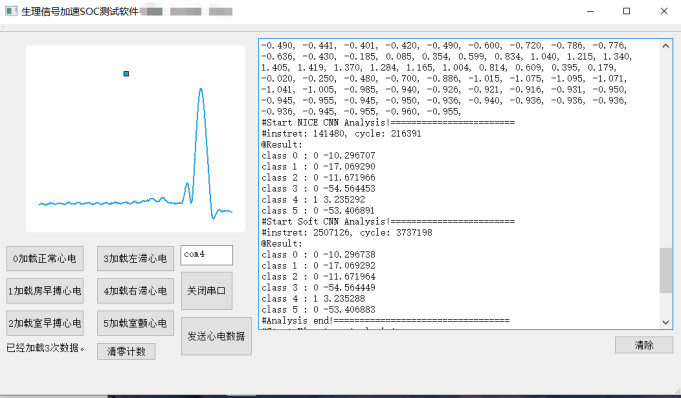

在上位机和协处理器联调过程中,为了提高分类精度和方便移植网络,以及测试CNN加速效果的下限,我们没有采用上述测试CNN网络,而是更换了一个具有1层卷积层、3层全连接层的结构,并将心电采样点数缩减到了250点。由于全连接层过多,频繁读内存的延迟会拖累算法整体计算速度,CNN加速效果降低为18倍左右,如图所示:

上位机和协处理器联调

由于全连接层占大多数的网络结构只是权宜之计,大多数网络依然会采用卷积层丰富的结构,因此基本可以判定18倍是协处理器在1维CNN计算加速的下限。

综上,本项目s的协处理器可以有效加速近似熵算法和一维卷积神经网络算法,有效解决熵和CNN融合算法计算量过大的问题,并且这两种算法可以应用于多种生理信号的分析,因此该协处理器的应用范围广泛,市场前景明朗。

4、BOM清单

| Comment | Description | Designator | Footprint | LibRef | Quantity |

| 0.1uF | 贴片陶瓷电容0603 | C1, C2, C3, C4, C7, C10, C23, C99, C128 | LC-0603_C | CAP_0603 | 9 |

| 0.1uF | 贴片陶瓷电容0402 | C5, C6 | LC-0402_C | CAP_0402 | 2 |

| 16pF | 贴片陶瓷电容0603 | C8, C11, C12 | LC-0603_C | CAP_0603 | 3 |

| 10uF | 贴片陶瓷电容0603 | C9, C13 | LC-0603_C | CAP_0603 | 2 |

| 100nF/16V | 贴片陶瓷电容0402 | C14, C15, C16, C17, C18, C19, C20, C21, C22, C27, C28, C29, C32, C33, C34, C35, C36, C37, C38, C39, C40, C41, C42, C43, C44, C45, C46, C47, C48, C49, C50, C51, C55, C58, C59, C69, C70, C71, C72, C73, C79, C80, C84, C85, C86, C87 | LC-0402_C | CAP_0603 | 46 |

| 100nF/16V | 贴片陶瓷电容0603 | C88 | LC-0603_C | CAP_0603 | 1 |

| 100uF/25V | C89 | CAP-SMD_BD6.3-L6.6-W6.6-FD | CAP_ELEC | 1 | |

| 100uF | 贴片陶瓷电容1206 | C90, C91 | LC-1206_C | CAP_1206 | 2 |

| 22uF | 贴片陶瓷电容0805 | C92, C93, C94, C95, C105, C107, C108, C110, C111, C113 | LC-0805_C | CAP_0805 | 10 |

| 22pF | 贴片陶瓷电容0603 | C96 | LC-0603_C | CAP_0603 | 1 |

| 22uF/16V | 贴片陶瓷电容1206 | C97, C98 | LC-1206_C | CAP_1206 | 2 |

| 470nF | 贴片陶瓷电容0603 | C100 | LC-0603_C | CAP_0603 | 1 |

| 22nF | 贴片陶瓷电容0603 | C101, C102, C103, C104 | LC-0603_C | CAP_0603 | 4 |

| 100nF | 贴片陶瓷电容0805 | C106, C109, C112 | LC-0805_C | CAP_0805 | 3 |

| 1uF | 贴片陶瓷电容0603 | C114, C115 | LC-0603_C | CAP_0603 | 2 |

| 100nF/50V | Capacitor | C116, C117, C118, C125 | LC-0603_C | CAP | 4 |

| 0.1uF/16V | Capacitor | C119, C122 | LC-0603_C | Cap | 2 |

| 10pF/16V | Capacitor | C120, C121, C126, C127 | LC-0603_C | CAP | 4 |

| 1nF/2KV | Capacitor | C123 | LC-1206_C | CAP | 1 |

| 1uF/16V | Capacitor | C124 | LC-0603_C | CAP | 1 |

| 5103308-1 | CN10 | IDC-TH_5103308-1 | 5103308-1 | 1 | |

| 10uF/16V | CT1 | LC-CASE-B_3528 | ELECTRO1 | 1 | |

| LED_0603 | 贴片LED_0603 | D1 | LC-0603_LED_S3 | LED_0603 | 1 |

| SMBJ5.0A | 瞬态抑制二极管 | D2, D8, D9 | LC-SMB(DO-214AA)_S4 | TVS | 3 |

| RED | 贴片LED_0603 | D3, D4, D5, D6, D7 | LC-0603_LED_S3 | LED_0603 | 5 |

| HX25003-2A | FAN1, ISO1, P4 | CONN-TH_2P-P2.50_HX25003-2A | HX25003-2A | 3 | |

| BLM18PG221SN1 | FB1, FB2 | LC-0603_L | FB0603 | 2 | |

| Header 4 | Header, 4-Pin | GND | HDR1X4 | Header 4 | 1 |

| HR911105A | J1 | RJ45_HR911105A | HR911105A | 1 | |

| MTB110-14S | JTAG1 | IDC-TH_MTB110-14S | JTAG_14P | 1 | |

| 1.5uH | L1 | IND-SMD_L7.0-W6.6_MCW-0650-220 | LOOP_0650 | 1 | |

| 4.7uH | L2, L3, L4 | IND-SMD_L7.0-W6.6_MCW-0650-220 | LOOP_0650 | 3 | |

| GREEN | 贴片LED_0603 | LED1 | LC-0603_LED_S3 | LED_0603 | 1 |

| Header 16 | Header, 16-Pin | P2 | HDR1X16 | Header 16 | 1 |

| 4.7K | 贴片电阻0603, Resistor | R1, R2, R3, R4, R6, R8, R9, R62, R99 | LC-0603_R | RES_0603, Res2 | 9 |

| 330 | 贴片电阻0603 | R5 | LC-0603_R | RES_0603 | 1 |

| 220 | 贴片电阻0603 | R7 | LC-0603_R | RES_0603 | 1 |

| 100R/1% | 贴片电阻0402 | R10 | LC-0402_R | RES_0402 | 1 |

| 1K/0.1% | 贴片电阻0603 | R11, R12 | LC-0603_R | RES_0603 | 2 |

| 240R/1% | 贴片电阻0402 | R13 | LC-0402_R | RES_0402 | 1 |

| 1K | 贴片电阻0603 | R14, R15, R16, R17, R18, R19, R20, R21, R22, R24, R26, R28, R30, R32, R34, R36, R38, R40, R42, R44, R46, R48, R50, R106 | LC-0603_R | RES_0603 | 24 |

| 820 | 贴片电阻0603 | R52 | LC-0603_R | RES_0603 | 1 |

| 0 | 贴片电阻0603 | R53, R63 | LC-0603_R | RES_0603 | 2 |

| 100 | 贴片电阻0603 | R54 | LC-0603_R | RES_0603 | 1 |

| 510 | 贴片电阻0603 | R55, R56 | LC-0603_R | RES_0603 | 2 |

| 10K | 贴片电阻0603, 名称:贴片电阻;规格型号:RC0603-103-J;厂家:通用;阻值:10k;精度:±5%, Resistor | R57, R58, R59, R60, R61, R64, R69, R75, R79, R80, R81, R82, R92, R102, R103, R104, R105 | LC-0603_R | RES_0603, Res2 | 17 |

| 150K | 贴片电阻0603 | R65 | LC-0603_R | RES_0603 | 1 |

| 100K/1% | 贴片电阻0603 | R66, R72 | LC-0603_R | RES_0603 | 2 |

| 100K | 贴片电阻0603 | R67 | LC-0603_R | RES_0603 | 1 |

| 5.1K | 贴片电阻0603 | R68, R71 | LC-0603_R | RES_0603 | 2 |

| 150K/1% | 贴片电阻0603 | R70 | LC-0603_R | RES_0603 | 1 |

| 53.6K/1% | 贴片电阻0603 | R73 | LC-0603_R | RES_0603 | 1 |

| 33K/1% | 贴片电阻0603 | R74 | LC-0603_R | RES_0603 | 1 |

| 75K/1% | 贴片电阻0603 | R76 | LC-0603_R | RES_0603 | 1 |

| 56K/1% | 贴片电阻0603 | R77 | LC-0603_R | RES_0603 | 1 |

| 10K/1% | 贴片电阻0603 | R78 | LC-0603_R | RES_0603 | 1 |

| 49.9R/1% | 名称:贴片电阻;规格型号:RC0603-103-J;厂家:通用;阻值:10k;精度:±5% | R83, R84, R96, R97 | LC-0603_R | Res2 | 4 |

| 22R | Resistor | R85, R86, R87, R88, R89, R90, R91, R95, R98, R101 | LC-0603_R | Res2 | 10 |

| 330R | Resistor | R93, R100 | LC-0603_R | Res2 | 2 |

| 12.1K/1% | 名称:贴片电阻;规格型号:RC0603-103-J;厂家:通用;阻值:10k;精度:±5% | R94 | LC-0603_R | Res2 | 1 |

| HX25003-5A | RS1 | CONN-TH_5P-P2.50_HX25003-5A | HX25003-5A | 1 | |

| Header 2 | Header, 2-Pin | S1, S2, S3, S4, S5 | HDR1X2 | Header 2 | 5 |

| Button_5.2*5.2*1.5 | 轻触按键 | SW1, SW2 | KEY-TH_4P-L6.0-W6.0-P3.90-LS7.8 | Button | 2 |

| TestPin | 测试点 | T1, T2 | TESTPIN | TestPin | 2 |

| XC7A100T-2FGG676I | Artix-7 FPGA, 300 User I/Os, 8 GTP, 676-Ball BGA, Speed Grade 2, Industrial Grade, Pb-Free | U1 | FGG676 | XC7A100T-2FGG676I | 1 |

| N25Q128A13ESE40F | U2, U4 | SOIC-8_L5.3-W5.3-P1.27-LS8.0-BL | N25Q128A13ESE40F | 2 | |

| MT41K128M16JT-125:k | 96ball,14mm*8mm | U3 | FBGA-96_L8.0-W14.0_TL | MT41K128M16JT-125:k | 1 |

| CH340E | U5 | MSOP-10_L3.0-W3.0-P0.50-LS5.0-BL | CH340E | 1 | |

| IL3122-3E | RS422接口芯片 | U6 | SOIC-16_L9.9-W3.9-P1.27-LS6.0-BL | IL3122-3E | 1 |

| MP8712 | U7 | QFN-14_MP8712 | MP8712 | 1 | |

| TPS563201 | U8, U9, U10 | SOT-23-6_L2.9-W1.6-P0.95-LS2.8-BR | TPS563201 | 3 | |

| LAN8720A | U11 | QFN24 | LAN8720A | 1 | |

| SRV05-4 | U12 | SOT-23-6_L2.9-W1.6-P0.95-LS2.8-BR - duplicate | SRV05-4 | 1 | |

| KH-TYPE-C-16P | USB1 | USB-C-SMD_KH-TYPE-C-16P | KH-TYPE-C-16P | 1 | |

| 50MHz | 7050有源晶振 | X1 | OSC-SMD_4P-L7.0-W5.0-BL | 7050 | 1 |

| 32768 | 7050有源晶振 | X2 | OSC-SMD_4P-L7.0-W5.0-BL | 7050 |

1 |