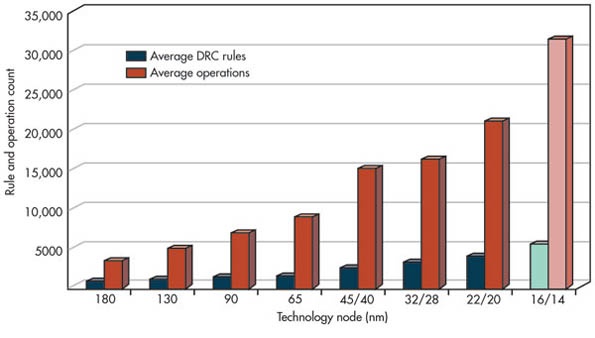

如果只是科普/大流程的话,从20年前硅片的制作流程就没怎么变过,唯一对芯片设计造成比较大的影响的是随着MOS管变小增加的DesignRule

我来简单的说一下模拟电路和数字电路设计/制作方面的差别吧:

首先明确一点:所有的ASIC(Application-SpecificIntegratedCircuit),也即应用芯片,都是有一个Design的目的,如果是在工厂里就是乙方提的要求;在PhD生涯里就是老板布置的活。。。

要成功通关,待我细细道来:

小怪:数字电路电路图

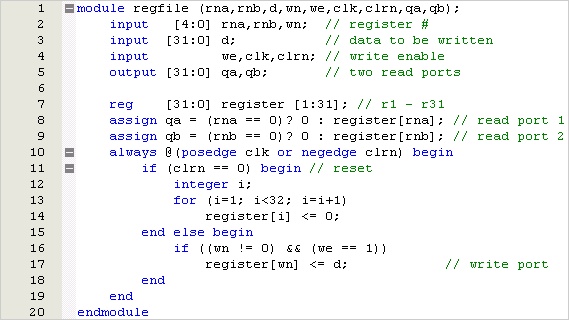

推荐武器:Verilog

数字电路一般用Verilog写,主要是因为方便(我才不告诉你我手动垒StandardCell呢)。比如说CPU级别的芯片,动辄上亿的MOS管,就算一秒画一个,不计连线时间,你得画38个月。

小怪:数字电路仿真推

荐武器:VCS,MMSIM

写完了Verilog,就要跑数字仿真了。一般会用到Synopsys的VCS或者MentorGraphics的MMSIM之类的。

这个仿真非常快,因为每一个MOS管都被看成是开关,然后加上一些非常粗糙的模拟出来的延迟时间。目的是看你写出来的玩意能不能正常工作。

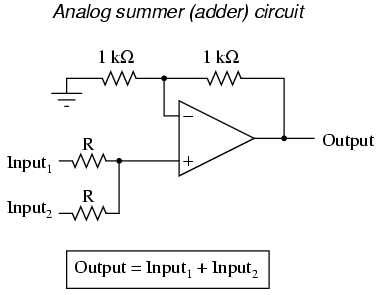

小怪:模拟电路电路

图推荐武器:Cadence(允许准确击打),SPICE(自由度高,可长可短)等

这个就比较复杂了。因为模拟电路的自由度非常高!比方说,一个MOS管在数字电路条件下就是一个开关,但是在模拟电路里面,根据栅极电压和电路结构不一样,分分钟完成开路-大电阻-放大器-电流源-导通各种功能。

所以呢,模拟电路基本就得手画了。

小怪:模拟电路仿真

推荐武器:Spectre(精度最高),HSPICE,PSpice,HFSS等

最好跟打小怪:模拟电路电路图小怪用一样的武器。

模拟电路的仿真包括但不限于:调节分压,仿真,模拟工作点等。。。而且千万记住!设计过程中,精细(Swing<=100mV)的模拟电路要做噪声分析!不然各种地方的噪音分分钟教你做人。。。

好,现在假设我们有电路图啦~

数字电路的电路图长这样:

模拟电路的电路图长这样:

下一步,就是要把这些东西变成实实在在的电路:

小Boss:综合电路:

推荐武器:DesignCompiler(DC)

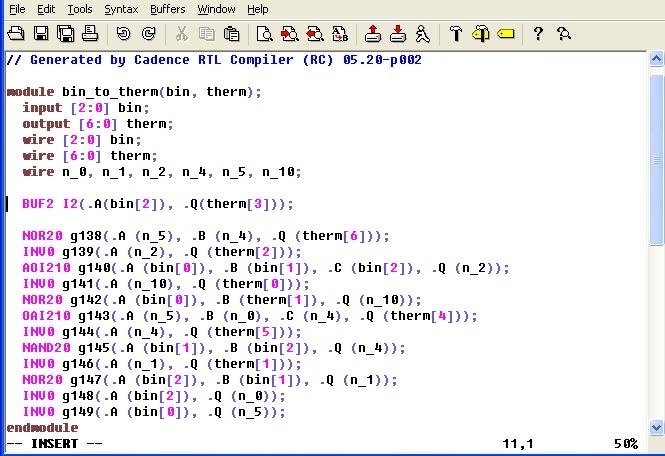

数字电路需要用到DesignCompiler,Synopsys公司出的大杀器,一招把Verilog转成Verilog!

这一步叫做Synthesis(综合)。

综合出来的电路也是Verilog格式,但是长这样:

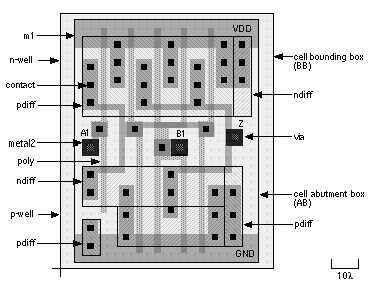

把一堆描述性质的语言转换成真正的StandardCell(标准门电路)StandardCell长这样:

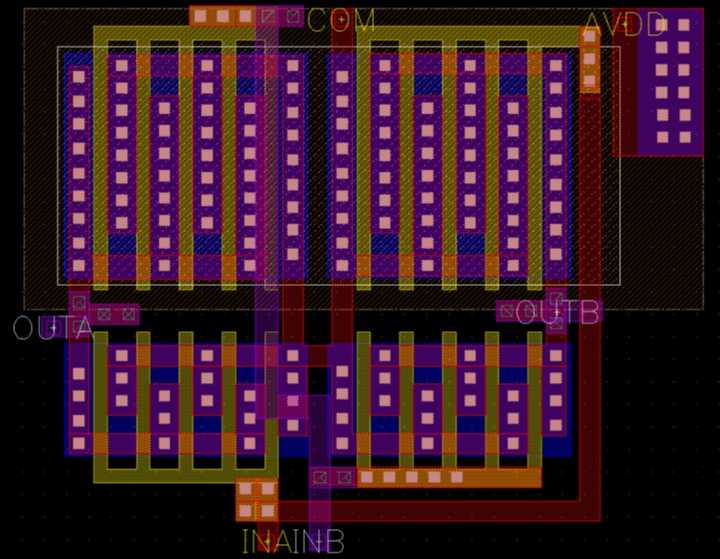

小Boss:模拟电路Layout

必杀:无。但是血厚。

推荐武器:CadenceLayoutEditor等。

模拟电路就比较烦了,一般会手画,大概长这样:

这一个是比较规整的Design,来个不规整的:

师兄有云:画模拟电路的Layout是体力活。我表示师兄说的太对了!

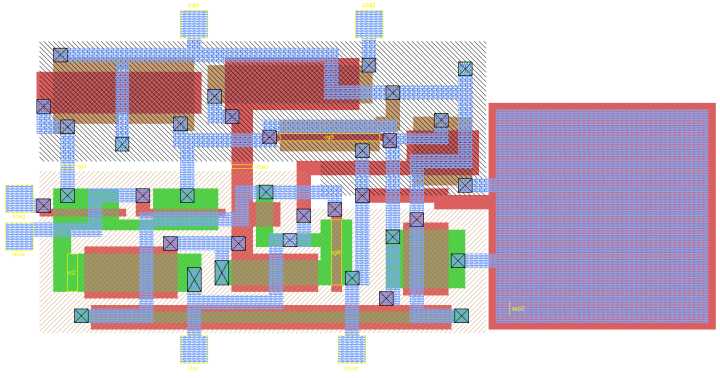

小Boss:数字电路Layout

必杀:向门神告状(DRC/LVSFail)。

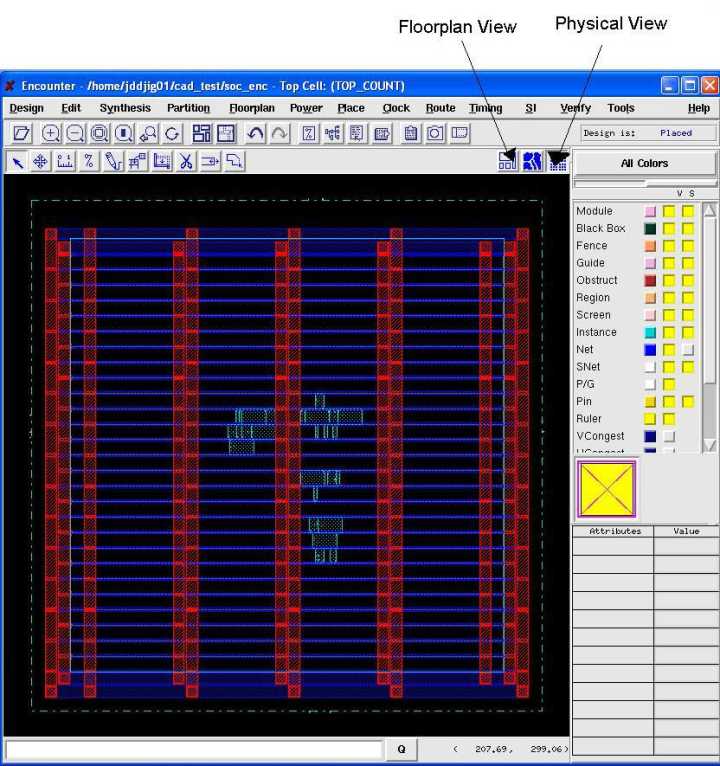

推荐武器:IC-compiler,Encounter

数字电路接下来就需要PlaceandRoute(布线)了。一般这个步骤由IC-Compiler/Encounter等工具来完成。具体就是,把综合过的Verilog中的每个StandardCell找到对应的StandardCellLayout,布置在用户指定的范围内,然后自动连线。

这个自动连线就很讲究:

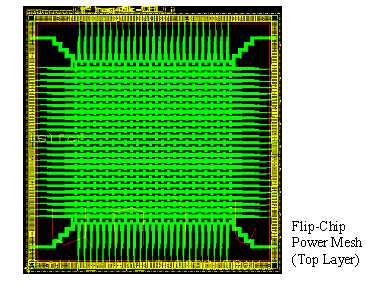

自动布线要先连时钟信号,然后连电源网络,最后连其他的数字信号等。

时钟信号默认会使用双倍线宽,如有分支,尽量使用对称的结构;

然后使用用户的方式架设电源网络。为什么叫电源网络呢?因为一般片上的电源长这样:

powernet这名字不是白起的。。。

自动布线就不展开讲了。。。

学问太多了(主要是制作工艺。。。)

之后,还有一个很重要的步骤:FillerCell

什么意思呢?

数字电路的StandardCell放完了,连好线了,大致长这样:

图中的那几个淡蓝色的Cell就是StandardCell,连线未显示。

你要敢把这个Design交到Fab去做,人家分分钟咒你全家。

为什么呢?打个比方:我想让你帮我剪一个窗花,给你一张A4纸(大概58800mm2),然后说,我想要剪个窗花,但是窗花的总面积不要超过1mm2,最好还要有镂空,有个人。。blahblahblah。。。

恩。差不多一个意思。。

所以为了让厂家和你不要那么难过,需要在片上没东西的地方加上Filler,也就是长得像StandardCell但是里面就是一坨没有连线的金属和轻掺杂层的东西。

之后,两大门神决定了你能不能提交:

门神1:DesignRuleCheck(DRC)

必杀1:AreaXXtoosmall

必杀2:XXtoXXmustbegreaterthanorequalto 0.038

推荐武器:CalibreRVE,ASSURA,仔细检查+喊师兄帮忙

每一招都对应的是(由于技术原因或者安全原因)无法被制作出来的部分。。

想击败他必须一招都不能中(NoDesignRuleViolation)。

门神2:LayoutVersusSchematiccheck(LVS)

必杀:LayoutdoesnotmatchSchematic。

推荐武器:CalibreRVE,ASSURE,喊老板帮忙

恩。就是确定你画的这个奇形怪状的Layout跟一开始的电路图是对的上号的。

虽然此门神仅有一招,但是这招千变万化,难以招架。

两大门神都开心了之后,你就可以把你做出来的这个GraphicDatabaseSystemII(GDSII)文件交到厂商的手里了。

从Fab回来以后,战斗还没结束。。

Boss:Bonding&Packaging(封装)

必杀:两个pad黏一块儿了!!!,pad金属掉了!!!,金属丝断了!!!。

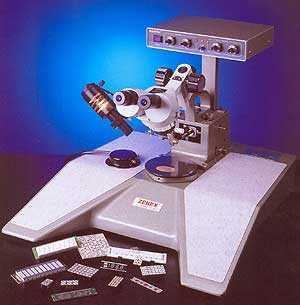

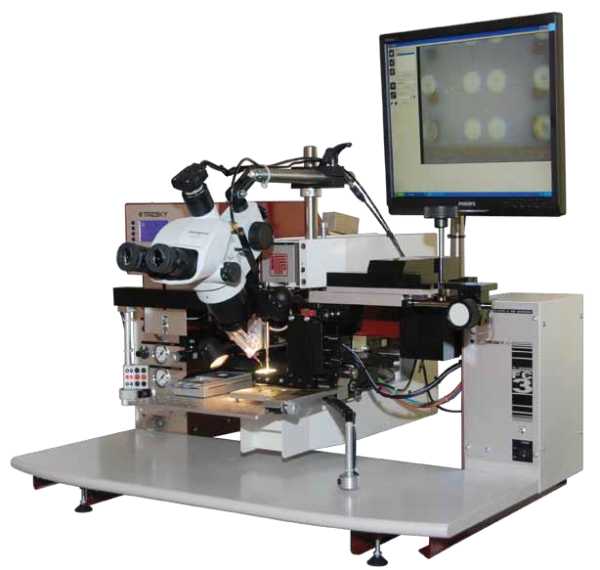

基础武器:BondingMachine

凡人即使有武器,挑战这个Boss也属不易。需要花重金升级武器才行,比如说:

实在不行,亦可祭出大杀器:让厂商Bond!这一步,将芯片变成我们认识的模样:

从:

变成:

Boss:PCBDesign

必杀:信号太多,面积太小;驱动太弱,电容太大;烧Chip。

推荐武器:AltiumDesign,Eagle等。

做出了Chip之后,就需要画一个配套的PCB,将外围电路在板上搭建好,或者引至其他外设等。

最终Boss:SystemDesign

必杀:此Boss神通广大,一切外部设备都可以唤来作为必杀。

推荐武器:Thebestweaponistheonebetweenyourears。USEIT。

最终,我们需要这个芯片在应用中展现它的实力,所以一个不满足需求的芯片就是渣渣。

| CA-IS3720LS/数字隔离器 | 0.7648 | |

| CA-IS3722HS/数字隔离器 | 77.6 | |

| CA-IS3740HW/数字隔离器 | 2.85 | |

| CA-IS3742HW/数字隔离器 | 3.12 | |

| CS48505S/RS-485/RS-422芯片 | 0.500355 | |

| CA-IS3721HS/数字隔离器 | 0.8974 | |

| CA-IS3720HS/数字隔离器 | 0.9234 | |

| XL1509-5.0E1/DC-DC电源芯片 | 0.7999 | |

| BSMD1812-200-30V/自恢复保险丝 | 0.38069 | |

| FS55X106K101EGG/贴片电容(MLCC) | 1.29 |

50万+现货SKU

品类不断扩充中

科技智能大仓储

最快4小时发货

正品有保障

物料可追溯

明码标价节省时间

一站式采购元器件