一、简介

漏电断路器因所处的供电节点不同,对漏电特性的要求也不同,因而对应着不同的国家或行业标准。国家标准方面,如:GB/T 16916,GB16917,GB/T 37751,GB/T 6829,GB/T 22794,GB/T 28527,GB/T20044 等等,及相关行业标准,如JB/T 8979, JB/T10494等等,而这些标准大多参考IEC、ISO、ITU等国外标准而设定。这些标准对漏电保护器的漏电流大小、漏电流最小不关断延时,最大延时,浪涌,群脉冲等等特性及实验方法做了约束。

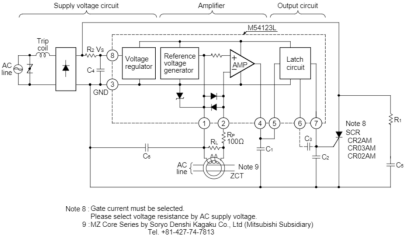

图1 天正电气的漏电保护器产品

自2015年矽源半导体进入低压电器行业以来,在漏电保护芯片方面已经涵盖了AC型、AC+S型、A型、A+S型、A+6型、B型等等,满足大部分客户的基本要求。在与客户的技术交流过程中,常常出现的问题是,降压电阻值如何选取、可控硅选型与什么有关、输入滤波电容不清楚如何设置、反延迟如何设置、最小不驱动时间如何设置、浪涌过不了如何解决、反进线或下进线如何实现等问题。本文章将围绕客户的关注点进行分析介绍。

二、输入滤波电路设计

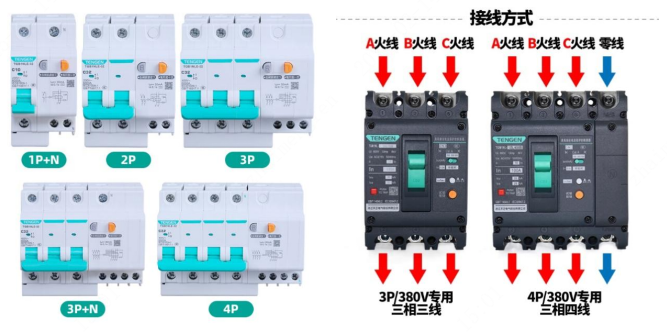

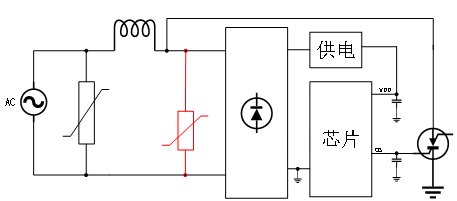

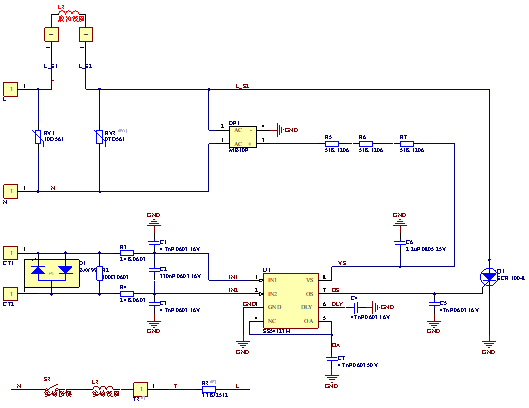

漏电保护器基于M54123L芯片的产品采用的单端滤波结构,如图2所示。这种方案对于单向的干扰信号具有一定的抑制作用,但是对于双向及电磁干扰的抑制能力较差,容易出现误跳问题。

图2 基于M54123L的漏电方案

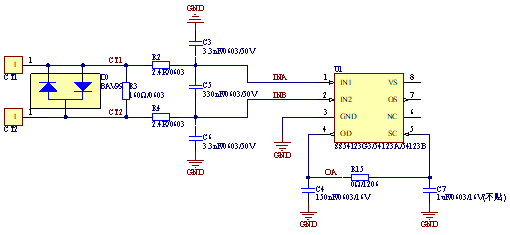

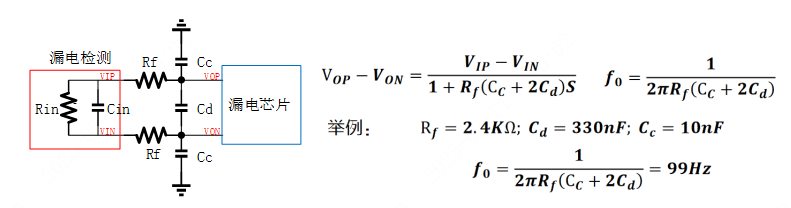

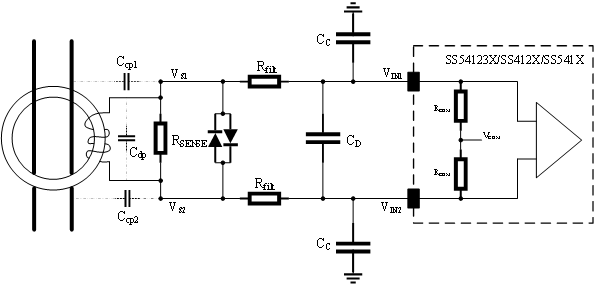

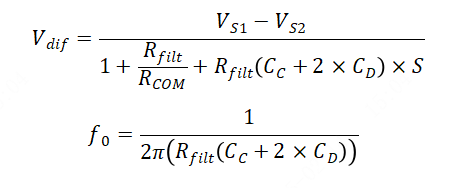

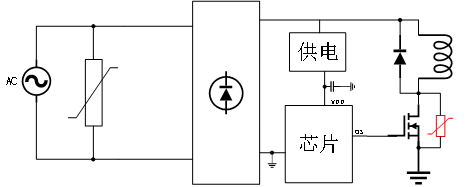

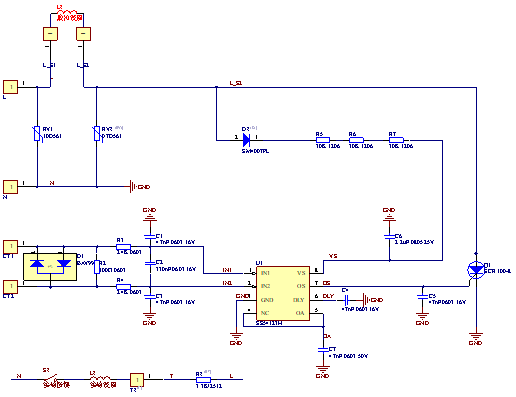

为了解决电磁干扰和双向干扰问题,业界开始采用差分滤波方案,如图3所示。

图3 漏电断路器互感器电流差分采集

差分采集部分包含互感器浪涌抑制双向二极管、采集电阻、滤波电阻和滤波电容,其中困扰工程师的问题是滤波电阻和滤波电容如何选择,本文将从理论和仿真方面做一个基本的介绍。图4和图5给出了互感器输出采样端到漏电芯片输入端口的滤波公式和波形(不考虑等效输入共模电阻)。

图4 差分输入网络公式推导

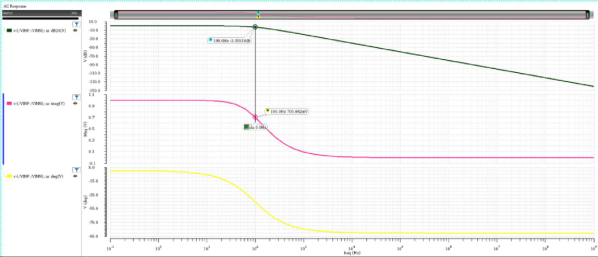

图5 差分输入网络的波特图

从频域仿真结果(图5)来看,理论与仿真是一致的。这时候工程师会问,是先确定滤波电阻呢还是滤波电容,有先后顺序吗?我们进一步进行理论分析。

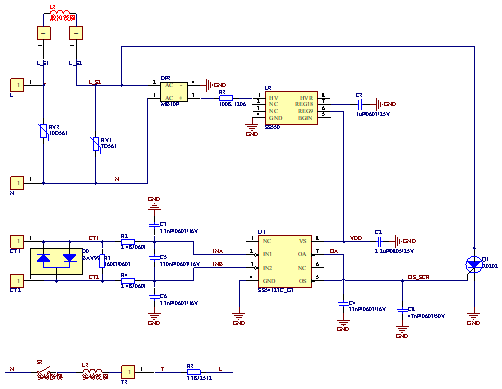

图6 矽源半导体漏电芯片等效共模电阻

我们采用图6的电路进行详细分析。图中包含了互感器与采样电路之间存在的寄生电容,以及考虑芯片中的输入共模电阻,从而可以更精确的对干扰网络进行分析。

当不存在漏电流时:

a. 静态状态:输入端口的差分电压VIN1-VIN2 = 0,输入端口的共模电压VIN1 = VIN2 = VCOM,且VS1=VS2=VCOM;

b. 动态状态:VIN1=VIN2=VCOM×[1/(RCOM×CC×S +1)];

c. 互感器干扰状态:Ccpx耦合进入芯片输入端口的电荷,被CC电容与Rfilt电阻形成的低通滤波器滤除,-3dB极点为1/(Rfilt×Cc)。当Ccp1和Ccp2电容大小不一致时,耦合产生不同同样会形成“假”漏电流(电网电压杂波干扰较大时容易出现此现象),引起产品误跳,因而需要选择合适的-3dB极点值,用于滤除干扰。

当存在漏电流时:

输入差分电压经过滤波网络在芯片输入端口产生如图4的差分电压:

综上所述,RCOM不但影响芯片输入端口的上电时间,同时影响差分输入信号的电压幅度。CC电容主要影响VINX的上电时间和电压稳定性,当RCOM较大时需要增大CC电容以保证输入端口电压的稳定,因而设计时在保证产品指标的同时,通过参数调整可以提升产品的整体性能。推荐的CC电容的范围1nF ~ 47nF。

Rfilt电阻的选择主要考虑芯片的共模电阻及驱动能力。设计时需要保证Rfilt不能太小,从而使共模驱动在正常范围内而不出现失真。通过公式推导可以得到ICOM=(VCOM + 0.5×ISENSE×RSENSE )/(Rfilt + RCOM)。同时选择Rfilt时也不能太大,会出现对输入信号的缩减,缩减比例为RCOM/(RCOM+Rfilt)。

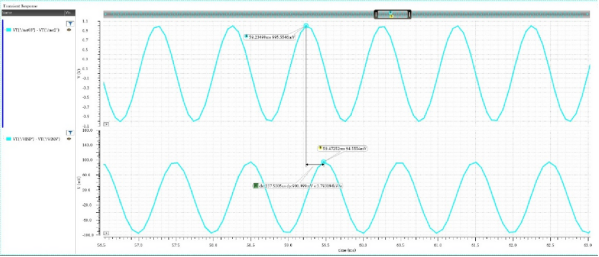

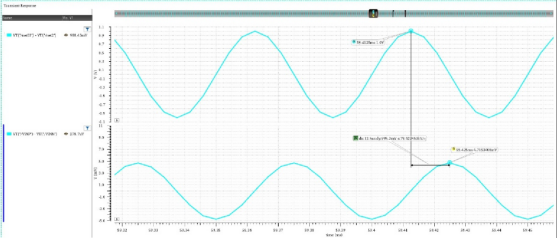

但是,当我们设计滤波网络,将-3dB极点设置到足够低时,如图4中的99Hz, 是不是就能滤除掉大于99Hz的高频漏电流影响呢?对于一倍漏电流是可以的,但是对于多倍漏电流,是很难的。对于图4中的例子,我们从时域的角度进行介绍。

图7 幅度1Vp-p,频率1KHz输入信号经过滤波后的波形

图7中,对于1Vp-p,1KHz的输入信号,经过-3dB极点为99Hz网络后,电压的幅度变为0.1V,仍然处于漏电保护器的识别范围,容易引起误跳。

图8 幅度1Vp-p,频率20KHz输入信号经过滤波后的波形

图8中,对于1Vp-p,20KHz的输入信号,经过-3dB极点为99Hz网络后,电压的幅度变为4.7mV,处于误跳的临界状态。

对于示例中的参数,对于高带宽漏电检测芯片,在100Hz时,滤波网络还有0.7倍左右的增益,输入频率为1Kz时,增益还有0.1倍。如果对于1KHz,幅度1V的输入信号,在芯片输入端还会存在0.1V的电压,同样会造成芯片误触发,因为漏电检测芯片的触发输入电压在5mV左右。输入频率高于20KHz时漏电芯片将不会响应,对于脉冲群测试,这个不响应频率至关重要,影响整个系统的指标。

结合国标的要求,对于普通的A或AC型漏电芯片,放大器带宽设计值在10KHz左右可以满足大部分的指标要求。同时针对逆变器和其他高频漏电流应用场景,推荐选用矽源的SS4125x系列高频抑制芯片,此芯片采用高通滤波电路来检测输入信号的频率,当频率高于100Hz时,芯片将对输入值做无效处理,不需要较大的外围阻容滤波电路。

三、延时时间设计

漏电断路器设计时,一个重要的指标就是时间,包括最小不驱动时间和最大关断时间。而最大关断时间随输入漏电流大小的不同,需要形成反延时特性。这对于漏电芯片的选择至关重要。

3.1 反延时时间设计

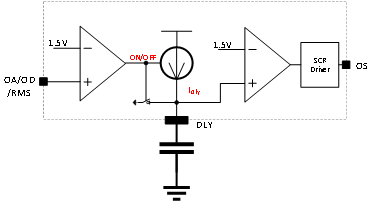

矽源半导体的漏电产品,均采用电容积分策略实现反延时特性,具体有两种实现方式:线性放大积分和比较触发积分。

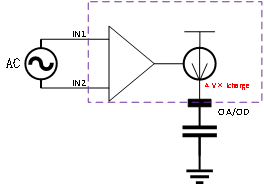

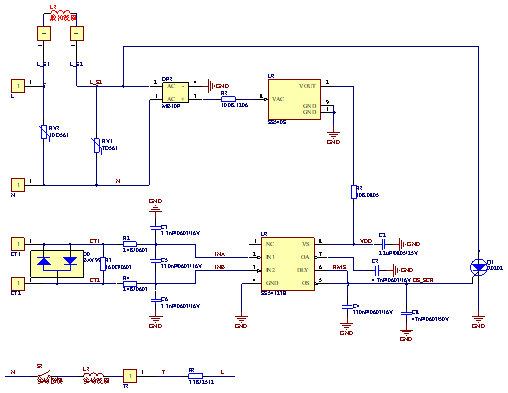

线性放大积分如图9所示,当输入信号幅度越高时,产生的充电电流越大,将加快对电容进行充电。当OA/OD的电压达到比较器比较电压后,触发可控硅驱动,进行脱扣操作。

图9 线性积分反延时设计

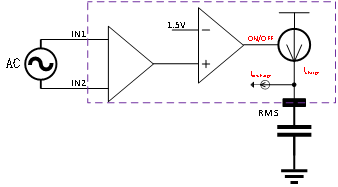

比较触发积分电路如图10所示,当输入信号幅度高于比较器阈值电压(如1.5V)时,开启充电电流(此充电电流值为固定值)对RMS引脚的电容进行充电,当幅度低于比较器阈值电压时,关闭充电电流,RMS脚被内部泄放电流泄放电荷。矽源半导体漏电产品的充电电流是泄放电流的10倍左右,从而形成典型的充放电过程。

反延时特性的实现通过开启与关断占空比来实现。当输入漏电流幅度较大时,高于比较器阈值电压的时间较长,此时对RMS电容的充电时间较长,将更快达到可控硅触发比较器的阈值,形成反延时特性。

图10 比较触发积分电反延时设计

3.2 最小不驱动时间设计

对于S型和延迟型产品,国标中有明确规定最小不驱动时间要求,这个最小不驱动时间就是由外部延时电路实现的。矽源半导体的最小不驱动时间电路如图11所示,当OA/OD端口,或RMS端口的积分电压高于1.5V时,将触发延时电流对外部电容进行恒定电流充电,当DLY端口的电压高于1.5V时,使能可控硅驱动电路,触发脱扣器工作。

图11 最小不驱动时间产生电路

这个延时在外部电容固定后,在整个漏电延时阶段产生恒定的延时特性,总延时为tDLY+tRMS的总和,研发人员在设计时需要特别注意。

3.3 闭合时间设计

漏电断路器延时设计时另外一个重要时间项目是闭合时间测试。虽然研发人员按照国标要求完成了缓变漏电流值测试、突发漏电延时测试,但是闭合时间测试会出现无法满足要求的情况,特别是5倍漏电流时,要求小于40ms的闭合时间测试。

影响闭合测试主要原因是整个测试系统的上电时间快慢问题。因突变测试时,系统已经上电,芯片已进入监控状态,所以可以快速进行漏电流的响应。而突变测试时,芯片的供电需要一定时间,因而需要电源供电设计能够快速的启动并稳定。

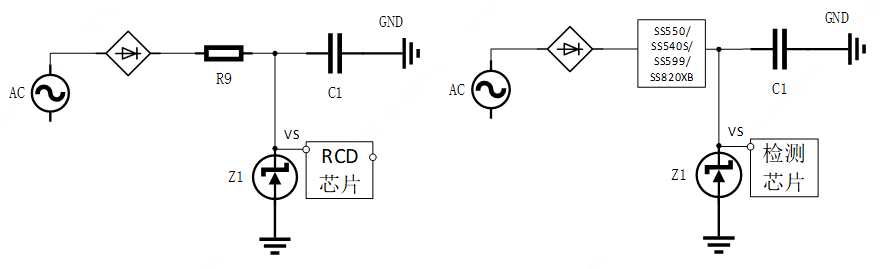

漏电检测目前较为常用的供电方式为电阻降压,这种方式成本最低,对于小电流的应用较为合适,但是对于采用单片机等功耗较大,或者输入电压范围较大的应用场合,电阻降压的发热劣势就非常明显。矽源半导体针对漏电产品,研发了高压线性供电芯片SS540S和SS550系列,高压电荷泵供电芯片SS56X和SS59X系列,高压非隔离ACDC供电芯片SS820XB系列,以及1500V高压非隔离微尺寸小功率供电方案等,方便客户依据不同的应用场景进行选择。

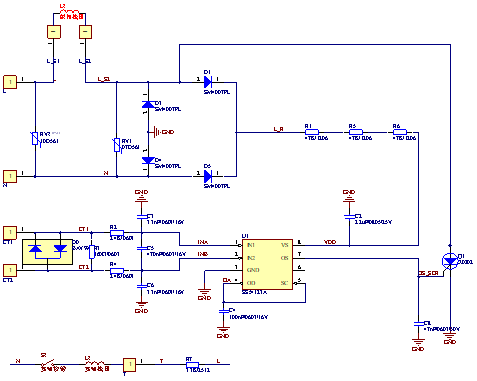

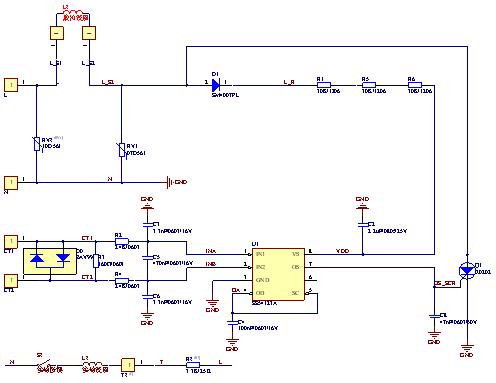

(a)传统电阻降压 (b)专用供电芯片

图12 漏电芯片供电方案

四、可控硅和高压MOS驱动设计

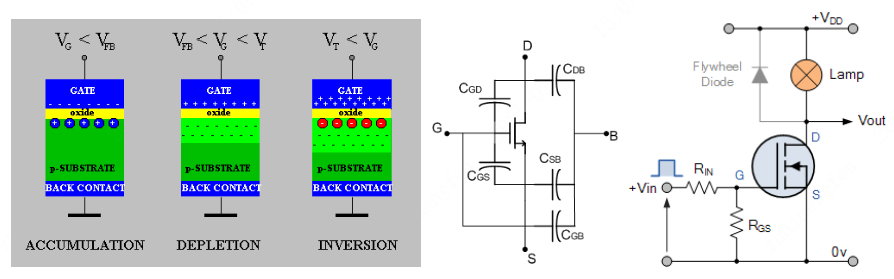

可控硅属于流控电子器件,MOS属于压控电子器件,针对不同的器件,在驱动选择时需要注意。矽源半导体针对两种脱扣线圈触发器件具有电压和电流两种类型的驱动可选择。

电压驱动型:

MOS,GaN,SiC,IGBT等属于压控型器件,主要通过施加电场在器件导通区域形成导电通道,从而实现器件的导通与关断,无静态开关电流,只有瞬态开关电流(对器件寄生电容机型充放电引起的电流)。

图13 电压驱动型原理与电路

电流驱动型:

BJT,SCR等器件属于流控型器件,通过控制基区少数载流子的运动(微小电流变化),在电场的作用下形成发射区和集电区之间大量电子和空穴的流动,如图14所示。

图14 电流驱动型原理与电路

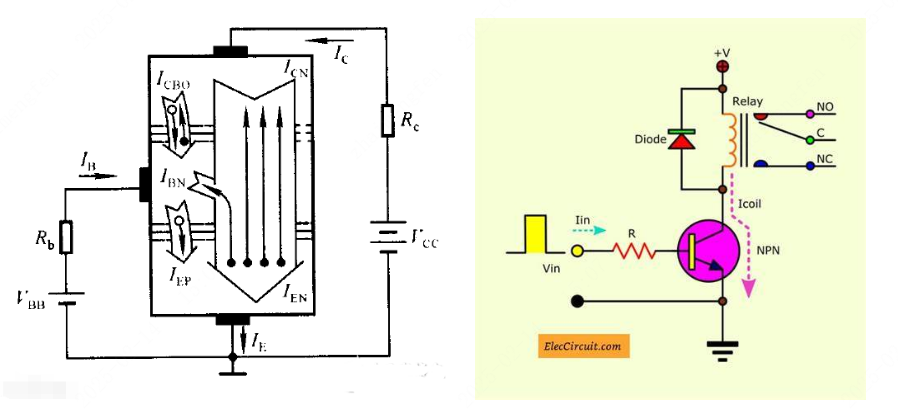

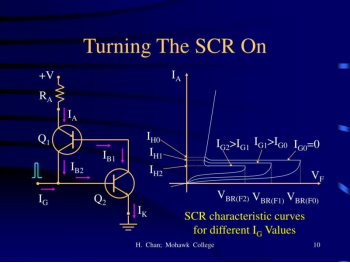

可控硅器件的工作分导通与关断,如图15和图16所示:

可控硅的导通,通过触发Q2工作,从而引起Q1的工作,之后形成Q1和Q2的正反馈过程。保证工作的条件:1. 驱动电压:>VTRIG;2.驱动电流:>ITRIG。

图15 可控硅的导通

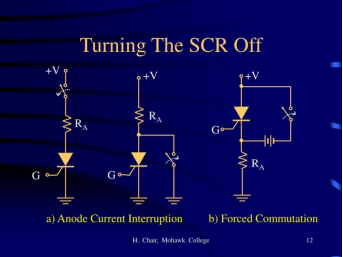

可控硅的截止有三种方法:

1. 在工作后断掉电流导通通路,并将GK电压拉低;

2. 将A端和K端拉成一个电平,并保持一段时间;

3. A端拉负压,将可控硅反偏工作,在一段时间内使导通电流消失的状态。

图16 可控硅的关断

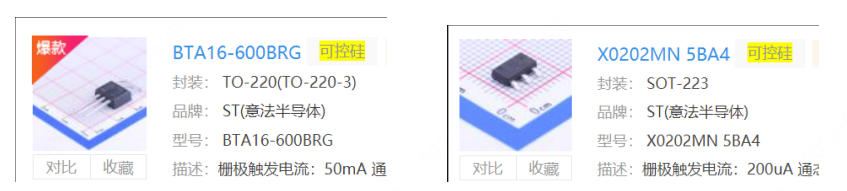

漏电保护中的可控硅选型考虑:

目前市面上常用的可控硅ITRIG电流从20uA ~ 50mA, VTRIG电压最大1.3V,如图17所示;驱动的选择直接由可控硅的驱动电流决定,同时芯片的供电状态决定了驱动的正常工作。对于两相漏电保护器,大多数采用性价比较高的100-8 型号,这种可控硅的最大触发电流为200uA 左右。

图17 常见可控硅型号和触发电流

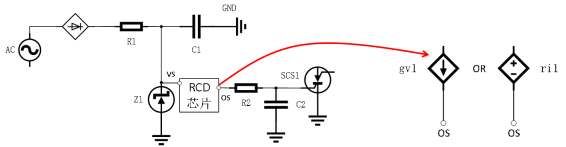

漏电保护器中采用成本较低的电阻降压方式,电阻R1的大小与RCD芯片自身的功耗以及可控硅的ITRIG电流有关。驱动部分采用压控和流控两种方式,如图18所示。

图18 电阻降压可控硅驱动方式

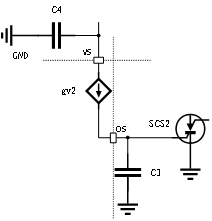

电流驱动细节分析:电流模式,采用最大电流驱动模式来驱动可控硅工作,如图19所示。

优点:1. 最大电流限定,对VS端口外部电容选型只用考虑驱动电流和芯片自身;2. 对稳压电容值C4需求不高。

缺点:1. 只能针对特定的可控硅,应用受限;2. 驱动可控硅的延迟时间受C3电容影响较大。

图19 可控硅电流驱动方式

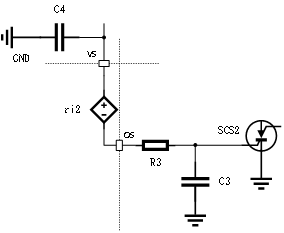

电压驱动细节分析:

电压模式,采用恒压来驱动可控硅工作,驱动电流大小由器件导通特性决定,如图20所示。

优点:

1. 驱动能力强,可以适应多种ITRIG电流的可控硅;

2. 压摆率大,驱动上升和下降时间快,驱动延迟小。

缺点:

在电阻降压型供电时,需要增加限流电阻或者采用其他稳压源供电。

图20 可控硅电压驱动方式

无论是电压驱动还是电流驱动,研发人员设计时需要关注VS供电部分的稳定性,因为芯片供电不稳定会造成芯片复位而无法充分实现脱扣器的正常脱扣。

五、反进线与下进线问题

1. 反进线

当前大部分的漏电产品,供电由负载端提供,当漏电触发后,断路器断开,此时漏电监控系统将失去电源,这种应用要求用户完全遵守进线与出线不能出现错误连接时。如果用户将进线接到漏电保护器的出线端,此时当发生漏电时,断路器脱扣,但是漏电检测系统的电源仍然存在,此时对于传统未做处理的漏电系统,可控硅会一直接通,将脱扣线圈烧毁,同时伴随可控硅烧毁的情况。

2. 下进线

漏电保护器产品的一种应用场景是负载端是光伏或者储能设备,当发生漏电时,漏电断路器断开,但是储能或者光伏设备会出现反向供电,此时漏电监控系统仍然有电。这时的状态与反进线一样,区别是这个反向电压是直流电,对于可控硅这种器件,很难关断,从而造成脱扣线圈和可控硅烧毁。

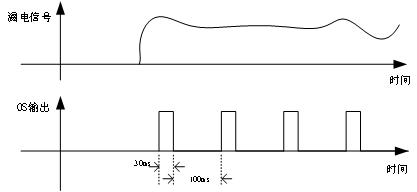

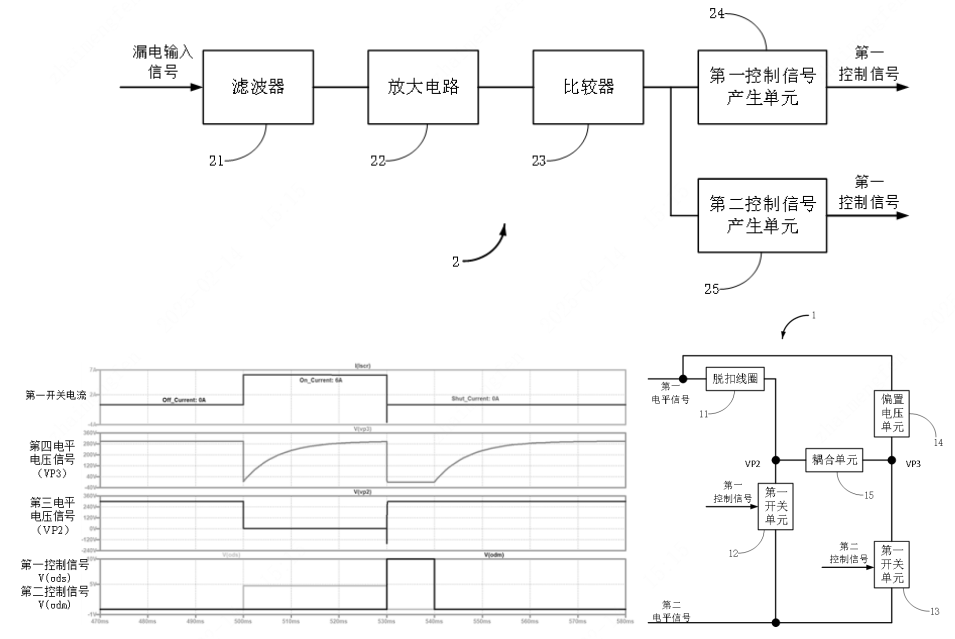

针对反接线与下进线问题,国矽微半导体提出的有限脉冲驱动策略(专利号: CN01922165706.4/CN01922167285.9)解决了可控硅及MOS应用中的问题。

当检测到漏电信号时,且漏电一直存在,可控硅或高压MOS驱动端(OS)将输出1~N次占空比为:30ms:100ms的控制信号,用于确保机构故障时不出现炸机问题。

图21 有限个数脉冲驱动

针对可控硅直流供电时的关断问题,国矽微半导体提出了一种专利策略(CN202010555350.X)

图22 国矽微半导体直流供电可控硅关断专利

六、浪涌特性设计优化

浪涌和群脉冲是漏电断路器产品研发中非常重要且经常遇到问题的两项测试,特别是浪涌。浪涌问题的解决不仅与器件有关,而且与PCBA的布局布线关系密不可分。不只是线路连接的问题,更多的要考虑瞬态高压或高电流产生的di/dt和dv/dt问题。常用的抑制方法是增大压敏的抑制能力或在浪涌通路中增加抑制电阻等策略,但是这种策略需要更多的PCB空间,对于对空间要求更高的产品需要寻找其他更合适的策略。

对于可控硅作为脱扣触发器件,在L/N线增加压敏电阻后,常采用脱扣线圈的大电感值来滤除浪涌脉冲对控制系统的影响。但是针对不同的应用场景,脱扣线圈的电感值变化范围较大,对浪涌电流的抑制会随着电感值的减小而减弱,常用的成本最低的解决办法如图23所示,在脱扣线圈之后增加一个压敏电阻。

图23 可控硅方案浪涌性能优化方案

对于采用MOS晶体管作为脱扣触发器件,因MOS器件属于压控器件,在脱扣触发器件,需要较大的瞬态能量和持续时间,因而大部分应用不能将脱扣线圈放在最前方,因为脱扣期间会造成控制芯片供电不足而不断复位,出现振铃型干扰信号。通常将脱扣线圈放到MOS驱动支路,且在驱动MOS上并联压敏电阻,以吸收浪涌能量而不会损坏MOS器件,如图24所示。

图24 MOS方案浪涌性能优化方案

七、矽源半导体漏电产品方案

1. 1P+N产品(脉冲触发)

图25 基于SS54123A的全桥整流1P+N方案

图26 基于SS54123A的半波整流1P+N方案

图27 基于SS54123H的全桥整流1P+N方案

图28 基于SS54123H的半波整流1P+N方案

2. 2P产品(电平/脉冲触发)

图25-28可用于2P产品,且图25-26中的SS54123A改为SS54123实现电平驱动模式。

图29 基于SS54123C与SS550的节能A型漏电方案(静态功耗小于50mW)

图30 基于SS54123E与SS540S的节能A型漏电方案(静态功耗小于75mW)

3. 3P/4P产品

采用SS54123、SS54123A、SS54123F、SS54123B、SS54123H、SS54123E等可实现3P/4P方案,如图31和32所示。

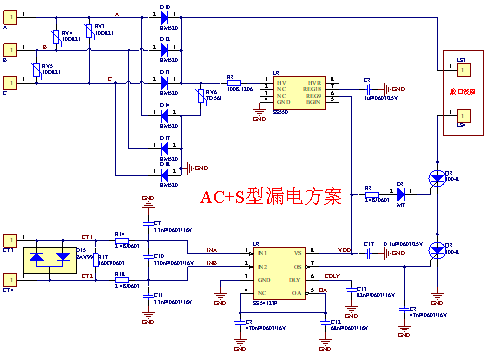

图31 基于SS54123F和SS550的AC+S型3P节能漏电方案

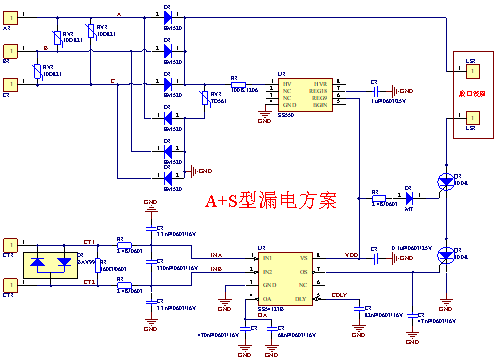

图32 基于SS54123B和SS550的A+S型3P节能漏电方案

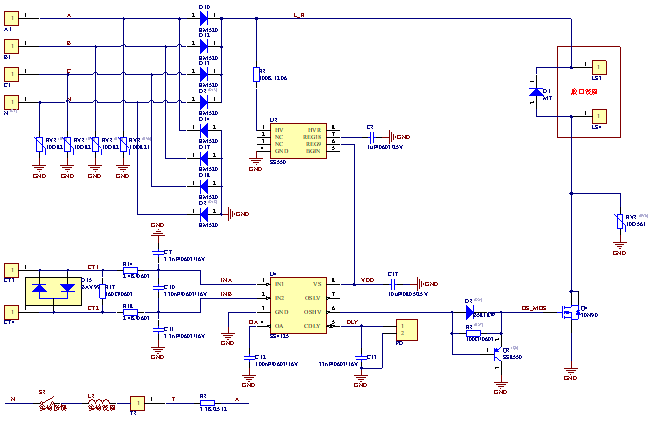

针对下进线应用,这里介绍一款高频漏电抑制的节能控制方案,如图33所示。

图33 基于SS4125B与SS550的4P下进线节能控制方案

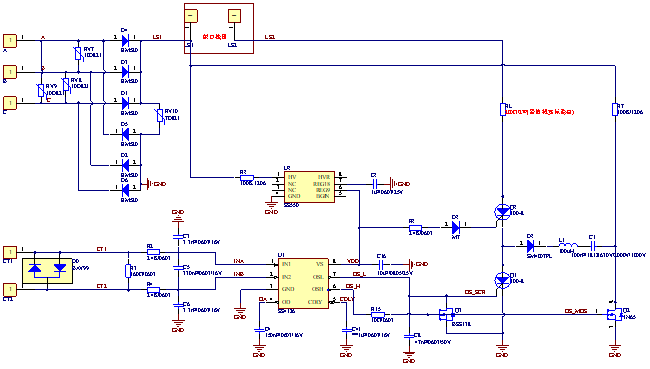

图34 基于SS4126B与SS550的3P可控硅关断型下进线节能控制方案

4. 4P智能产品

图35 基于SS4125B、SS4450B与SS820X的低压脱扣器4P AC型下进线节能智能方案

图36 基于SS4127、SS4450B与SS820X的低压脱扣器4P A型下进线节能智能方案

5. 输入高压智能产品

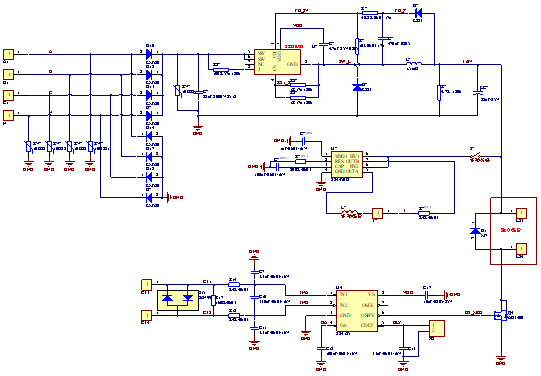

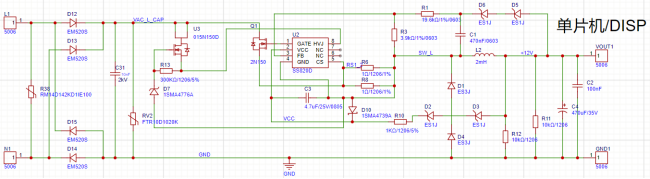

高压智能产品,主要的瓶颈是高压供电,特别是交流输入电压高于600VRMS时,因为SS820XB系列最高芯片耐压900V,对于浪涌等实验,残压会高于1000V,为此矽源半导体开发了高压快速供电套片,由OSM2N150,SS820D,SS820XB和OSMD015N150等核心器件实现。其他漏电部分的检测与控制与前面介绍的5种方案类似,同时此供电方案配合单片机可实现不同应用场景的智能检测与控制方案。

图37 基于OSMD015N150、SS820D与OSM2N150的高压快速交直流供电

图37的高压供电方案适合直流和交流输入,两种输入情况下,整个电源的效率及发热均在可控的范围内。

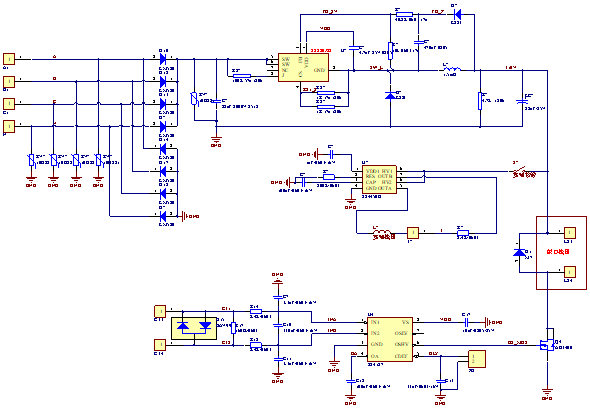

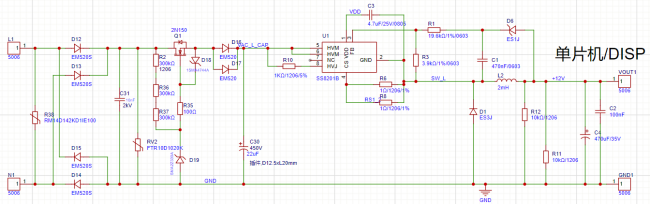

图38 基于SS8201B与OSM2N150的高压快速交流供电

图38的供电方案适合于交流输入应用,在高压输入时,2N150工作在交流预稳压状态,当输入电压高于稳压二极管(D19)电压时,2N150对VAC_L_CAP提供一个钳位电压,此时2N150工作,会产生发热;当输入电压低于D19的稳压值时,VAC_L_CAP跟随输入,2N150发热忽略不计,整个过程中,2N150的发热与输出负载关系密切。

|

产品类型 |

商品编号 |

矽源芯片 |

规格 |

触发类型 |

方案类型 |

|

1P+N/2p产品 |

SS54123 |

SOP8 |

电平触发 |

全桥/半波整流 AC型漏电方案 |

|

|

SS54123A SS54123H |

SOP8 |

脉冲触发 |

|||

|

2P产品 |

SS54123C SS550 |

SOP8 ESOP8 |

脉冲触发 |

节能型A型漏电方案 (静态功耗小于50mW) |

|

|

SS54123E SS540S |

SOP8 ESOP8 |

脉冲触发 |

节能型A型漏电方案 (静态功耗小于75mW) |

||

|

3P/4p产品 |

SS54123F SS550 |

SOP8 ESOP8 |

脉冲触发 |

AC+S型3P节能漏电方案 |

|

|

SS54123B SS550 |

SOP8 ESOP8 |

A+S型3P节能漏电方案 |

|||

|

下进线产品 |

SS4125B SS550 |

SOP8 ESOP8 |

脉冲触发 |

4P下进线节能控制方案 |

|

|

努力上架中 |

SS4126B SS550 |

SOP8 ESOP8 |

3P可控硅关断型 下进线节能控制方案 |

||

|

4p智能 产品 |

努力上架中 |

SS4125B SS4450B SS820X |

SOP8 |

脉冲触发 |

低压脱扣器4P AC型 下进线节能智能方案 |

|

努力上架中 |

SS4127 SS4450B SS820X |

SOP8 |

低压脱扣器4P A型 下进线节能智能方案 |

||

|

输入高压 智能产品 |

努力上架中 |

OSMD015N150+SS820D+OSM2N150 |

SOP8、TO252/TO263 |

- |

高压快速交直流供电 |

|

努力上架中 |

SS8201B OSM2N150 |

SOP8、TO252/TO263 |

- |

高压快速交流供电 |